# High Performance Organic Nonvolatile Flash Memory Transistors with High-Resolution Reduced Graphene Oxide Patterns as a Floating Gate

Dae Sung Chung,\*,† Sung Min Lee,† Jang Yeol Back, $^{\$}$  Soon-Ki Kwon, $^{\$}$  Yun-Hi Kim,\*,† and Suk Tai Chang\*,†

ABSTRACT: High-performance organic nonvolatile memory transistors (ONVMTs) are demonstrated, the construction of which is based on novel integration of a highly conductive polymer as a semiconductor layer, hydroxyl-free polymer as a tunneling dielectric layer, and high-resolution reduced graphene oxide (rGO) patterns as a floating gate. Finely patterned rGO, with a line width of 20–120  $\mu$ m, was embedded between SiO<sub>2</sub> and the polymer dielectric layer, which functions as a nearly isolated charge-trapping center. The resulting ONVMTs demonstrated ideal memory behavior, and the transfer characteristics promptly responded to writing and erasing the gate bias.

In particular, the retention time of written/erased states tended to increase as the rGO line width was reduced, implying that the line width is a critical factor in suppressing charge release from rGO. Using a 20- $\mu$ m-wide rGO pattern, a nonvolatile large memory window (>20 V) was retained for more than 5 × 10<sup>5</sup> s, which is 50 times longer than non-patterned rGO films.

KEYWORDS: organic devices, nonvolatile memory devices, reduced graphene oxide, thin films, micropatterning, charge-trapping layers

# ■ INTRODUCTION

Electrically reprogrammable and preferably nonvolatile memory devices based on organic materials have continued to grow over the past decade because of their distinct advantages, such as solution processability, light-weight, low cost, and the possibility of being integrated with printed electronics on a plastic substrate. 1-10 Organic memory devices can be categorized into various types according to their operating mechanisms, such as resistive switching devices, <sup>2,3</sup> ferroelectric dielectric devices, <sup>6,7</sup> and floating gate devices. <sup>8,9</sup> Among these, floating gate devices, which are operated by capacitance modulation of the trapping sites in the floating gate, are particularly attractive because their memory characteristics can be easily tuned by strategically selecting and/or engineering the trapping sites. In such organic nonvolatile memory transistors (ONVMTs), metallic nanoparticles are one of the most frequently used trapping sites because of their quantumconfined characteristics, which considerably reduce the possibility of charge loss from a nanoparticle to the underlying dielectric layer. 10 A limiting factor, owing to the use of nanoparticles as a floating gate, is the relatively narrow memory window due to the inherent band gap restriction.<sup>11</sup>

Graphene oxide (GO) can be another floating gate candidate because oxidized GO domain has a wide band-gap that can act as an effective charge trapping site. <sup>13</sup> In fact, GO sheets have been successfully integrated into inorganic <sup>13</sup> and even organic <sup>12</sup> memory devices as charge-trapping layers, resulting in non-

volatile large memory windows. Recently, a reduced graphene oxide (rGO) layer partially covering a 3-aminopropyltriethoxysilane (APTES) treated substrate was used as a charge-trapping layer in a nonvolatile memory device. Although further investigations are required to understand the charge trapping effect of rGO flakes, their structural defects and residual oxygen functional groups are considered to act like charge trapping sites in memory devices. Nonetheless, earlier reports have mainly focused on the use of GO or rGO sheets as charge trapping centers for increasing the memory window. Thus far, there have been no attempts to confine these charge-trapping centers to enhance the nonvolatile properties of memory devices.

With that in mind, we show that line-patterned rGO (with fine line width) can be much better charge trapping centers for ONVMTs without compromising the large memory window in nonvolatile memory operations. Novel ONVMTs are fabricated using a highly conductive polymer as the semiconductor layer, hydroxyl-free polymer as the tunneling dielectric layer, and patterned rGO thin film as the floating gate. In this study, we have used highly stable polymeric semiconductors, i.e., poly[2,5-bis(2-octyldodecyl)pyrrolo[3,4-c]pyrrole-1,4(2H,5H)-dione-(E)-1,2-di(2,2'-bithiophen-5-yl)ethene] (PDPPDBTE),

Received: March 28, 2014 Accepted: May 20, 2014 Published: May 20, 2014

<sup>&</sup>lt;sup>†</sup>School of Chemical Engineering and Materials Science, Chung-Ang University, Seoul 156-756, Republic of Korea

<sup>&</sup>lt;sup>‡</sup>Department of Chemistry and RINS, Gyeongsang National University, Jinju 660-701, Republic of Korea

<sup>§</sup>School of Materials Science and Engineering and ERI, Gyeongsang National University, Jinju, 660-701, Korea

as well as a hydroxyl-free polymer dielectric, i.e., Cytop. These elements together allow a threshold voltage  $(V_{\rm th})$  shift that originates only from the rGO because the trapping sites in semiconductors have a negligible effect even after air/electrical exposure. Following the analysis of transfer characteristics under repeated writing and erasing gate bias, we demonstrate large threshold voltage shits (Memory window >15 V). More importantly, we show that the memory retention time of ONVMTs with line-patterned rGO thin films tends to increase as the line width of patterned rGO decreases, thereby resulting in a retention time greater than  $5 \times 10^5$  s when a 20- $\mu$ m line pattern was used.

# EXPERIMENTAL SECTION

Preparation of rGO Thin Film. An aqueous GO solution produced by the Hummers method<sup>17</sup> was obtained from Graphene Supermarket (New York, U.S.A.). The GO dispersion was centrifuged at 8000 rpm for 10 min to remove unexfoliated flakes (WiseSpin CF-10, Daihan Scientific), followed by mixing with ultrapure Milli-Q water to obtain a GO solution with a concentration of 2.4 mg mL<sup>-1</sup>. Uniform rGO thin films on  $Si/SiO_2$  substrates were prepared using the meniscus-dragging deposition (MDD) technique. <sup>18</sup> Briefly, a glass microscope slide ( $25 \times 75 \text{ mm}^2$  with plain end, Fisher Scientific) and Si/SiO<sub>2</sub> wafer, which are used as a deposition plate and coating substrate, respectively, were hydrophilized with a piranha solution for 30 min and rinsed with DI water. Once the deposition plate was in contact with the coating substrate at an angle of 30°, a 40-µL drop of GO solution was injected between the two plates. The deposition plate was pushed in place with an alternating motion generated by a motorized stage (AL1-1515-3S, Micro Motion Technology) with a constant speed of 20 mm s<sup>-1</sup>. The deposition was repeated 20 times (one alternating back-and-forth motion is defined as one deposition). The resulting GO films was reduced using hydriodic (HI) acid vapor at 80 °C for 3 h, yielding thin rGO films.

Formation of rGO Patterns. An Si wafer was coated with SU-8 25 photoresist (MicroChem, Inc.) to a thickness of 20  $\mu$ m using a spin-coater (ACE-200, Spin Coater). A photo mask containing line-pattern printouts was placed onto the SU-8 photoresist layer and was exposed to UV light (UVCURE-60PH, Lichtzen). The UV-exposed photoresist was treated in SU-8 developer solution (MicroChem, Inc.). Polydimethylsiloxane (PDMS) prepolymer (Sylgard 184, Dow Corning) was cast onto the photoresist master to prepare the prepatterned elastomeric molds used for patterning the rGO films. After curing them at 70 °C for 6 h, the PDMS molds were peeled off from the master. The rGO film and the pre-patterned PDMS mold were exposed to air plasma (PDC-32G, Harrick Plasma) for 20 s at a power of 6.8 W and for 90 s at 18 W, respectively, before being brought into contact with each other for several minutes. After removing the PDMS molds, high-resolution rGO line-patterns were formed on the Si/SiO<sub>2</sub> substrates.

**Device Fabrication.** ONVMTs were fabricated on a common gate of highly n-doped silicon with a 100-nm thick, thermally grown  $\mathrm{SiO}_2$  dielectric layer. After the rGO patterns were treated with UV ozone for 10-20 min, a thin layer of Cytop (Asahi Glass) was spin-coated onto the  $\mathrm{SiO}_2$  dielectric layer ( $\sim$ 20 nm). A solution containing PDPPDBTE was spin-coated at 2000 rpm from 0.7 wt % chloroform solutions to form thin films with nominal thickness of 50 nm, as confirmed by the surface profiler (Alpha Step S00, Tencor). The films were annealed at 200 °C for 10 min under a nitrogen atmosphere. Gold source and drain electrodes were evaporated on top of the semiconductor layers (60 nm). For all constructions, typical channel widths (W) and lengths (U) were 1600 and 160  $\mu$ m, respectively.

Characterization. Optical images of the rGO patterns were acquired by an Olympus BX-51 optical microscope mounted on a high-resolution ProRes CF Scan digital CCD camera (Jenoptik). The thickness of the rGO patterns was measured using an atomic force microscope (AFM) (XE-100, psia). The electrical characteristics of the fabricated devices were measured in air using Keithley 236 and

Keithley 2400 source/measure units combined with a home-built LabVIEW program. Gate bias signals at various frequencies were supplied by an arbitrary signal generator (AFG310, Tektronix), and the source-drain responses were recorded using either the LabVIEW program or a digital phosphor oscilloscope (TDS 5052, Tektronix) depending on the time scale.

# ■ RESULTS AND DISCUSSION

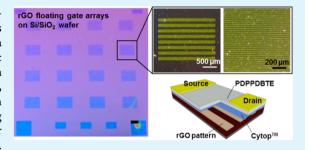

Figure 1 shows the procedures followed to prepare the linepatterned rGO floating gate for ONVMTs by applying the

**Figure 1.** Schematic illustration of line-pattern fabrication for a rGO film. (a) Fabrication of rGO thin film on  $Si/SiO_2$  substrate using the MDD technique. (b) Oxygen plasma treatment of pre-patterned PDMS mold and rGO film, and conformal contact between the two surfaces. (c) Removal of the PDMS mold. (d) ONVMT device with high-resolution rGO line-patterns. The inset of (c) shows the optical micrograph of line-patterned rGO arrays. The scale bar in the inset image is 1 mm.

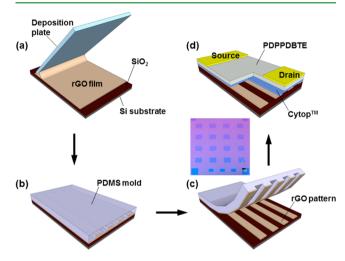

plasma-enhanced detachment patterning (PEDP) method. 19 This method begins with coating a uniform rGO thin film onto a hydrophilized Si/SiO<sub>2</sub> substrate using the MDD. Separately, a PDMS mold, containing stripe-shaped micropatterns, is prepared. Both the rGO film and PDMS mold are then exposed to oxygen plasma and subsequently brought into conformal contact without any additional pressure or heating. The exposure to oxygen plasma improves the work of adhesion between the rGO and PDMS surfaces by enhancing the surface polarity of both surfaces without significant damage to the rGO thin films at the relatively low power plasma condition used in this study. 19,20 Adhesion of such strength between the two surfaces can give a rise to selective detachment of the rGO film from the substrate, while peeling off the pre-patterned PDMS mold. The inset in Figure 1c shows the arrays of a linepatterned rGO on the Si/SiO<sub>2</sub> surface. Figure 2a-c shows the typical types of patterned rGO floating gates used in this study: film type, 120-µm-wide stripes, and 20-µm-wide stripes, respectively. The floating gates have uniform thickness of about 7 nm, as shown in Figure 2d. The as-prepared rGO floating gates used in the manufacturing of ONVMTs were assembled with thin layers of Cytop and PDPPDBTE conducting polymer, as shown in Figure 1d.

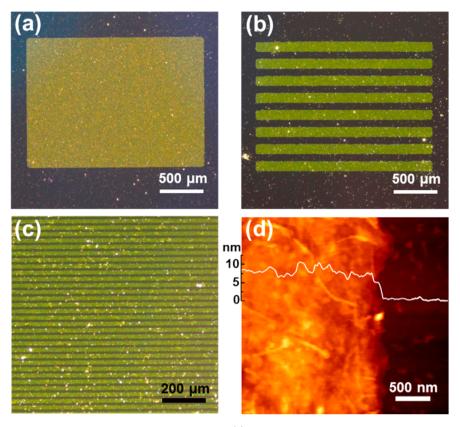

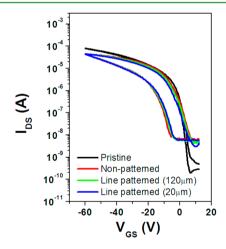

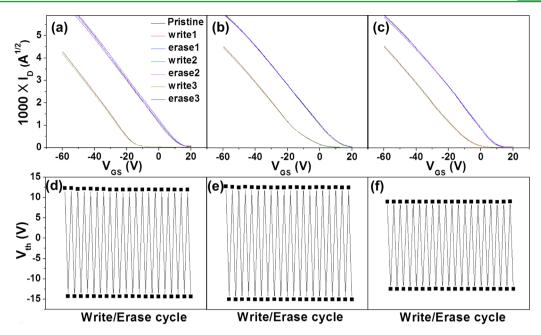

The fabricated ONVMTs with various types of rGO (non-patterned GO film, line-patterned rGO) displayed typical memory behaviors, as shown in Figure 3. The transfer characteristics (drain-source current vs gate voltage) of the

Figure 2. Optical microscope images of floating gate layers in ONVMTs. (a) rGO thin film and line-patterned rGO with width of (b) 120  $\mu$ m and (c) 20  $\mu$ m. (d) AFM image of the line-patterned rGO on a Si/SiO<sub>2</sub> substrate with a height profile.

**Figure 3.** Transfer characteristics of the various transistors used in this study. Both the forward and backward sweeps are included to illustrate the hysteresis windows of the devices.

ONVMTs without rGO, with non-patterned rGO film, and with line-patterned (20  $\mu$ m and 120  $\mu$ m) rGO are summarized after measuring under both forward and reverse gate sweeps. All the devices revealed reasonably high charge carrier mobility of 0.2–0.3 cm²/(V s). The observed low hysteresis for the rGO-free device and large hysteresis window (~20 V for non-patterned and ~15 V for line-patterned) for rGO-devices indicate the effective charge trapping ability of rGO. The larger hysteresis window of ONVMTs with non-patterned rGO, compared to that with line-patterned rGO, can be attributed to the larger effective area of the rGO being exposed to the upper deposited polymeric semiconductor. Note that line-patterned

rGO has  $\sim$ 40% smaller effective area than the non-patterned film, as shown in Figure 2a–c.

The performance of ONVMTs, used as electrically programmable and erasable memory devices, was evaluated by applying gate voltage pulses of fixed duration and measuring the corresponding transfer characteristics. In contrast to Si-flash memory devices, which operate with n-type MOSFETs, the written state of p-type ONVMTs, (where p-type polymeric semiconductors are used) corresponds to the moment when enough hole-charge carriers are stored in the rGO (floating gate), resulting in a negative shift in the threshold voltage  $(V_{th})$ . Conversely, the erased state can be defined as the moment when trapped hole charge carriers are flushed out of the rGOs, restoring  $V_{\rm th}$  to its original value. Figure 4a-c shows that the transfer functions of ONVMTs with non-patterned rGO film and line-patterned rGO were substantially shifted in the negative direction after applying a gate bias of -60 V. Reverse control of these transfer functions was also possible by applying a positive gate bias of 60 V. Furthermore, these memory characteristics were quite robust and reproducible. As shown in Figure 4d-f, during the 20 writing/erasing cycles, ONVMTs maintained memory windows of 27, 24, and 18 V for nonpatterned rGO, 120- and 20-µm-wide line-patterned rGO, respectively. The magnitude of programming voltage also has an effect on memory performance. For small gate bias of up to 10 V, the transfer characteristics remained nearly unchanged. Once the gate bias reach a critical value of ~15 V, however, the shift in  $V_{\rm th}$  becomes significant. This result is a very encouraging one because the negligible shift in  $V_{\rm th}$  at low programming voltage allows non-destructive read-out for flash memory applications. It is also notable that reasonable memory

Figure 4. (a)—(c) Transfer characteristic states of ONVMTs in a write/erase cycle of (a) non-patterned, (b) 120-µm-wide line-patterned, and (c) 120-µm-wide line-patterned rGOs. (d),(e) V<sub>th</sub> as a result of repeated write/erase cycles with the same sequence as in the upper panel.

Figure 5.  $V_{\rm th}$  as a function of (upper panel) writing and (lower panel) erasing voltage. (From left to right in each panel: non-patterned, 120- $\mu$ m-wide line-patterned, and 20  $\mu$ m-wide line-patterned rGO floating gates).

windows were obtained at low gate voltage ( $\sim$ 20 V) owing to the thin polymeric tunneling layer.

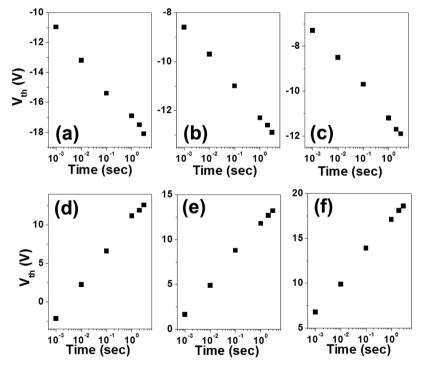

The trapping mechanism of the charge carriers was further characterized by investigating the shift of  $V_{\rm th}$  as a function of programming time. The change in  $V_{\rm th}$  is monitored while the write/erase time is increased, and the gate bias is kept constant at  $\pm 60$  V. In Si-flash memory transistors, incremental changes to the threshold voltage can be attributed to the time (t) dependence of the stored charge,  $^{21}$  i.e.,

$$\Delta V_{\rm th}(t) = -Q(t)/C$$

where Q and C are the total charge and capacitance of the dielectric layer, respectively. It is well known that regardless of the assumption of trap distribution or tunneling probability, charge trapping models predict a logarithmic time dependence of total charge<sup>22</sup> as follows:

$$Q \approx \ln(t/t_0)$$

Figure 5a—f shows the logarithmic dependence of  $V_{\rm th}$  on time under writing and erasing, respectively. Together with the above-mentioned theoretical description, these results support

that the memory operation of our ONVMT follows that of conventional Si-flash memory devices. Having trapped holes in rGO, which is a consequence of applying a negative gate bias, means that fewer holes are injected from the source to the channel during the transfer sweep (writing). Trapped holes are then released by applying a positive gate bias, thus no longer inhibiting hole injection from the source to the channel (erasing).

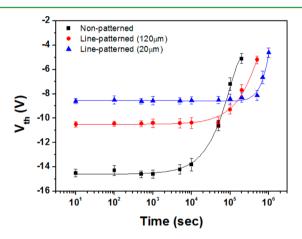

For nonvolatile memory applications, excellent retention ability is a key figure of merit. To investigate this behavior, the following measurements were conducted. After applying a writing gate bias (-60 V) under the conditions stated in Figure 3, the shifted  $V_{\rm th}$  was monitored as a function of time. Between the various measurement points, the device was kept in the dark without being exposed to electrical stress. As shown in Figure 6, in all the devices,  $V_{\rm th}$  was conserved for nearly  $10^4 \text{ s}$ ,

**Figure 6.** Retention time of various ONVMTs with non-patterned, 120- $\mu$ m-wide line-patterned, and 20  $\mu$ m-wide line-patterned rGO floating gates.

thereby implying slow relaxation of trapped charge carriers from rGO. After 10<sup>4</sup> s, V<sub>th</sub> of ONVMT with non-patterned rGO films started to display a rather drastic positive shift. Interestingly, however, ONVMT with line-patterned rGO revealed a much longer retention time of up to 10<sup>5</sup> s. Surprisingly, ONVMTs with a narrower line width (20  $\mu$ m) exhibited an even longer retention time, of up to  $5 \times 10^5$  s. One possible explanation for this is their discrete nature compared to non-patterned rGO films. The stored charge in a linepatterned rGO is in fact isolated, and any minor damage on a dielectric layer does not significantly affect the total stored amount of charge. Actually, this is the most important reason why small-sized nanoparticles with discrete nature are practically used for the floating gate of nonvolatile memory transistor. 11,24,25 The enhancement of retention using a narrower line pattern supports this agreement. Other reports with non-isolated graphene film and graphene oxide film yielded the rather shorter retention time of  $10^3 \sim 10^4$  s.  $^{12,23,27}$  In addition, in those earlier results, 12 which report the first ONVMT with GO as a floating gate, a rather thick tunneling dielectric layer was used to fully prevent the trapped charges from being released, which resulted in a retention time of 10<sup>4</sup> s. However, it is worthwhile to note that such a thick tunneling layer not only improves the retention behavior, but also increases the programming voltage. In our results, we combine a thin tunneling layer (Cytop ~20 nm) that allows a low programming voltage down to 20 V, and a patterned rGO that

enables a long retention time up to  $5 \times 10^5$  s. To the best of our knowledge, this is the first report on the long duration electrical stability of rGO-based organic memory devices achieved by strategic engineering of rGO. For comparison, other organic non-volatile memory devices that employed Au nanoparticles as a floating gate yielded retention times ranging from  $10^3$  to  $10^5$  s.  $^{27-30}$

# CONCLUSIONS

In summary, we have demonstrated high-performance organic nonvolatile memory transistors (ONVMTs) by introducing a high-resolution line-patterned rGO as an effective floating gate. The resulting rGO-based ONVMTs exhibits superior retention time as well as transfer characteristics that respond promptly to writing and erasing gate bias, compared to other graphene-based memory devices. The improvements are primarily attributed to the nearly isolated charge-trapping center of the finely patterned rGO. The patterning method described here is easy and scalable to large-area rGO floating gate arrays on rigid or flexible substrates. Thus, this technology can potentially play a key role in future electronic memory devices.

## AUTHOR INFORMATION

# **Corresponding Authors**

\*E-mail: dchung@cau.ac.kr. \*E-mail: ykim@gnu.ac.kr. \*E-mail: stchang@cau.ac.kr.

#### Notes

The authors declare no competing financial interest.

# ACKNOWLEDGMENTS

This Research was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIP) (2012047047) and Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (NRF-2013R1A1A2012177).

#### REFERENCES

- (1) Hwang, S. K.; Bae, I.; Kim, R. H.; Park, C. Flexible Non-Volatile Ferroelectric Polymer Memory with Gate-Controlled Multilevel Operation. *Adv. Mater.* **2012**, *24*, 5910–5914.

- (2) Scott, J. C.; Bozano, L. D. Nonvolatile Memory Elements Based on Organic Materials. *Adv. Mater.* **2007**, *19*, 1452–1463.

- (3) Tseng, R. J.; Huang, J.; Ouyang, J.; Kaner, R. B.; Yang, Y. Polyaniline Nanofiber/Gold Nanoparticle Nonvolatile Memory. *Nano Lett.* **2005**, *5*, 1077–1080.

- (4) Baeg, K. J.; Noh, Y. Y.; Ghim, J.; Kang, S. J.; Lee, H.; Kim, D. Y. Organic Non-Volatile Memory Based on Pentacene Field-Effect Transistors Using a Polymeric Gate Electret. *Adv. Mater.* **2006**, *18*, 3179–3183.

- (5) Katz, H. E.; Hong, X. M.; Dodabalapur, A.; Sarpeshkar, R. Organic Field-Effect Transistors with Podlarizable Gate Insulators. *J. Appl. Phys.* **2002**, *91*, 1572–1576.

- (6) Lin, J.; Li, W.; Yu, Z.; Yi, M.; Ling, H.; Xie, L.; Li, S.; Huang, W.  $\pi$ -Conjugation-Interrupted Hyperbranched Polymer Electrets for Organic Nonvolatile Transistor Memory Devices. *J. Mater. Chem.C* **2014**, *2*, 3738–3743.

- (7) Kang, S. J.; Bae, I.; Park, Y. J.; Park, T. H.; Sung, J.; Yoon, S. C.; Kim, K. H.; Choi, D. H.; Park, C. Non-Volatile Ferroelectric Poly(vinylidene fluoride-co-trifluoroethylene) Memory Based on a Single-Crystalline Tri-Isopropylsilylethynyl Pentacene Field-Effect Transistor. Adv. Funct. Mater. 2009, 19, 1609–1616.

- (8) Sekitani, T.; Yokota, T.; Zschieschang, U.; Klauk, H.; Bauer, S.; Takeuchi, K.; Takamiya, M.; Sakurai, T.; Someya, T. Organic Nonvolatile Memory Transistors for Flexible Sensor Arrays. *Science* **2009**, *326*, 1516–1519.

- (9) Leong, W. L.; Lee, P. S.; Lohani, A.; Lam, Y. M.; Chen, T.; Zhang, S.; Dodabalapur, A.; Mhaisalkar, S. G. Non-Volatile Organic Memory Applications Enabled by in-Situ Synthesis of Gold Nanoparticles in a Self-Assembled Block Copolymer. *Adv. Mater.* **2008**, *20*, 2325–2331.

- (10) Kim, S. J.; Lee, J. S. Flexible Organic Transistor Memory Devices. *Nano Lett.* **2010**, *10*, 2884–2890.

- (11) Talapin, D. V.; Lee, J. S.; Kovalenko, M. V.; Shevchenko, E. V. Prospects of Colloidal Nanocrystals for Electronic and Optoelectronic Applications. *Chem. Rev.* **2010**, *110*, 389–458.

- (12) Kim, T. W.; Gao, Y.; Acton, O.; Yip, H. L.; Ma, H.; Chen, H.; Jen, A. K. Y. Graphene Oxide Nanosheets Based Organic Field Effect Transistor for Nonvolatile Memory Applications. *Appl. Phys. Lett.* **2010**, *97*, 023310.

- (13) Wang, S.; Pu, J.; Chan, D. S. H.; Cho, B. J.; Loh, K. P. Wide Memory Window in Graphene Oxide Charge Storage Nodes. *Appl. Phys. Lett.* **2010**, *96*, 143109.

- (14) Rani, A.; Song, J. M.; Lee, M. J.; Lee, J. S. Reduced Graphene Oxide Based Flexible Organic Charge Trap Memory Devices. *Appl. Phys. Lett.* **2012**, *101*, 233308.

- (15) Eda, G.; Chhowalla, M. Chemically Derived Graphene Oxide: Towards Large-Area Thin-Film Electronics and Optoelectronics. *Adv. Mater.* **2010**, *22*, 2392–2415.

- (16) Chung, D. S.; Kang, I.; Kwon, S. K.; Kim, Y. H. Non-Volatile Hybrid Memory Devices with Excellent Reliability. *RSC Adv.* **2013**, *3*, 13156–13162.

- (17) Hummers, W. S.; Offeman, R. E. Preparation of Graphitic Oxide. J. Am. Chem. Soc. 1958, 80, 1339–1339.

- (18) Ko, Y. U.; Cho, S.; Choi, K. S.; Park, Y.; Kim, S. T.; Kim, N. H.; Kim, S. Y.; Chang, S. T. Microlitre Scale Solution Processing for Controlled, Rapid Fabrication of Chemically Derived Graphene Thin Films. *J. Mater. Chem.* **2012**, *22*, 3606–3613.

- (19) Kim, N. H.; Kim, B. J.; Ko, Y.; Cho, J. H.; Chang, S. T. Surface Energy Engineered, High-Resolution Micropatterning of Solution-Processed Reduced Graphene Oxide Thin Films. *Adv. Mater.* **2013**, 25, 894–898.

- (20) Kim, H.; Yoon, B.; Sung, J.; Choi, D. G.; Park, C. Micropatterning of Thin P3HT Films via Plasma Enhanced Polymer Transfer Printing. *J. Mater. Chem.* **2008**, *18*, 3489–3495.

- (21) Sewell, F. A. Charge Storage Model for Variable Threshold FET Memory Element. *Appl. Phys. Lett.* **1969**, *14*, 45.

- (22) Ferris-Prabhu, A. V. Charge Transfer by Direct Tunneling in Thin-Oxide Memory Transistors. *IEEE Trans. Electron. Dev.* **1977**, 24, 524–530.

- (23) Ji, Y.; Choe, M.; Cho, B.; Song, S.; Yoon, J.; Ko, H. C.; Lee, T. Organic Nonvolatile Memory Devices with Charge Trapping Multilayer Graphene Film. *Nanotechnol.* **2012**, *23*, 105202.

- (24) Lee, J. S. Nonvolatile Memory Devices Based on Self-Assembled Nanocrystals. *Physica E* **2013**, *51*, 94–103.

- (25) Lee, J. S. Progress in Non-Volatile Memory Devices Based on Nanostructured Materials and Nanofabrication. *J. Mater. Chem.* **2011**, 21, 14097–14112.

- (26) Park, Y.; Gupta, D.; Lee, C.; Hong, Y. Role of Tunneling Layer in Graphene-Oxide Based Organic Nonvolatile Memory Transistors. *Org. Electron.* **2012**, *13*, 2887–2892.

- (27) Kim, S. J.; Lee, J. S. Flexible Organic Transistor Memory Devices. *Nano Lett.* **2010**, *10*, 2884–2890.

- (28) Mabrook, M. F.; Yun, Y.; Pearson, C.; Zeze, D. A.; Petty, M. C. A Pentacene-Based Organic Thin Film Memory Transistor. *Appl. Phys. Lett.* **2009**, *94*, 173302.

- (29) Leong, W. L.; Mathews, N.; Tan, B.; Vaidyanathan, S.; Dötz, F.; Mhaisalkar, S. Solution Processed Non-Volatile Top-Gate Polymer Field-Effect Transistors. *J. Mater. Chem.* **2011**, 21, 8971–8974.

- (30) Han, S. T.; Zhou, Y.; Wang, C.; He, L.; Zhang, W.; Roy, V. A. L. Layer-by-Layer-Assembled Reduced Graphene Oxide/Gold Nano-

particle Hybrid Double-Floating-Gate Structure for Low-Voltage Flexible Flash Memory. *Adv. Mater.* **2013**, 25, 872–877.